1. Tujuan [KEMBALI]

a. Mengetahui apa itu J-K Flip-Flop dan T Flip-Flop

b. Mengetahui cara kerja J-K Flip-Flop dan T Flip-Flop

c. Melakukan simulasi J-K Flip-Flop dan T Flip-Flop

2. Alat dan Bahan [KEMBALI]

a. Gerbang AND

Gerbang AND adalah gerbang yang akan memiliki output berlogika 1 hanya jika semua inputnya berlogika 1 pula. Apabila terdapat salah satu inputnya berlogika 0 maka output gerbang akan berlogika 0.

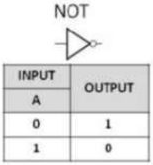

b. Gerbang NOT

Gerbang NOT adalah gerbang yang memiliki output berupa kebalikan dari inputnya. Apabila inputnya berlogika 0 maka outputnya akan berlogika 1, begitupun sebaliknya.

c. Gerbang NAND

Gerbang NAND adalah gerbang AND yang dihubungkan dengan gerbang NOT sehingga output dari gerbang ini merupakan kebalikan dari gerbang AND. Contohnya, jika gerbang AND memiliki output 0 dengan input 0 dan 1 maka gerbang NAND akan memiliki output bernilai 1 untuk input yang sama.

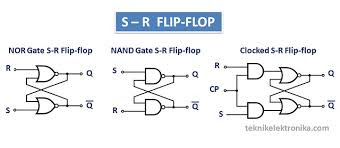

d. S-R Flip-Flop

S-R adalah singkatan dari “Set” dan “Reset”. Sesuai dengan namanya, S-R Flip-flop ini terdiri dari dua masukan (INPUT) yaitu S dan R. S-R Flip-flop ini juga terdapat dua Keluaran (OUTPUT) yaitu Q dan Q’. Rangkaian S-R Flip-flop ini umumnya terbuat dari 2 gerbang logika NOR ataupun 2 gerbang logika NAND. Ada juga S-R Flip-flop yang terbuat dari gabungan 2 gerbang Logika NOR dan NAND.

e. J-K Flip-Flop

J-K Flip-flop merupakan pengembangan dari S-R Flip-flop dan paling banyak digunakan. J-K Flip-flop memiliki 3 terminal Input J, K dan CL (Clock). Berikut ini adalah diagram logika J-K Flip-flop. Kelebihan JK Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti di beri berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluarannya / outputnya.

3. Dasar Teori [KEMBALI]

10.5 J-K Flip-Flop

J-K flip-flop berperilaku sama seperti flip-flop R-S kecuali untuk salah satu entri dalam tabel fungsi. Dalam kasus flip-flop R-S, kombinasi input S = R = 1 (dalam kasus flip-flop dengan input HIGH aktif) dan kombinasi input S = R = 0 (dalam kasus flip-flop dengan input RENDAH aktif) dilarang. Dalam kasus J-K flip-flop dengan input HIGH aktif, maka output dari matikan flip-flop, yaitu, beralih ke keadaan lain, untuk J = K = 1. Outputnya berubah menjadi J = K = 0 dalam kasus flip-flop yang memiliki input LOW aktif. Jadi, J-K flip-flop mengatasi masalah kombinasi input terlarang dari R-S flip-flop.

Gambar 10.26 (a) dan (b) masing-masing tunjukkan simbol rangkaian sandal jepit J-K yang dipicu level dengan input TINGGI dan RENDAH aktif, bersama dengan tabel fungsinya. Gambar 10.27 menunjukkan realisasi J-K flip-flop dengan R-S flip-flop.

Tabel karakteristik untuk J-K flip-flop dengan input J dan K TINGGI aktif dan J-K flip-flop dengan input LOW J dan K aktif masing-masing ditunjukkan pada Gambar 10.28 (a) dan (b). Sesuai peta Karnaugh ditunjukkan pada Gambar 10.28 (c) untuk tabel karakteristik Gambar 10.28 (a) dan pada Gambar. 10.28 (d) untuk tabel karakteristik Gambar 10.28 (b).

|

| Gambar 10.28 |

Persamaan karakteristik untuk peta Karnaugh masing-masing dari Gambar 10.28 (c) dan (d) sebagai berikut.

10.5.1 J-K Flip-Flop dengan Input PRESET dan CLEAR

Seringkali perlu untuk menghapus flip-flop ke status logika ‘0’ (Qn = 0) atau preset ke status logika ‘1’ (Qn = 1). Contoh bagaimana hal ini diwujudkan ditunjukkan pada Gambar 10.29 (a). Flip-flop dibersihkan (yaitu, Qn = 0) setiap kali input CLEAR adalah ‘0’ dan input PRESET adalah ‘1’. Flip-flop diatur sebelumnya ke status logika ‘1’ setiap kali input PRESET adalah ‘0’ dan input CLEAR adalah ‘1’. Di sini, CLEAR dan input PRESET aktif saat LOW. Gambar 10.29 (b) menunjukkan simbol rangkaian presetable ini, flip-flop J-K yang dapat dihapus dan memiliki clock. Gambar 10.29 (c) menunjukkan tabel fungsi dari flip-flop tersebut.

10.5.2 Flip-Flop Master – Slave

Gambar 10.30 (a) menunjukkan flip-flop master-slave yang dibangun dengan dua flip-flop J-K. Flip-flop pertama disebut master flip-flop dan yang kedua disebut slave. Jam untuk slave flip-flop adalah pelengkap jam untuk master flip-flop.

10.6 Toogle Flip-Flop

Output dari toggle flip-flop, juga disebut T flip-flop, berubah status setiap kali dipicu pada masukan T-nya, yang disebut masukan toggle. Artinya, keluaran menjadi '1' jika itu adalah '0' dan '0' jika itu adalah '1'. Gambar 10.34 (a) dan (b) masing-masing menunjukkan simbol rangkaian positif edge-triggered dan negative flip-flop T yang edge-triggered, bersama dengan tabel fungsinya.

10.6.1 J-K Flip-Flop sebagai Toggle Flip-Flop

Jika kita mengingat tabel fungsi flip-flop J-K, kita akan melihat bahwa, ketika input J dan K dari flip-flop terikat ke level aktifnya (level ‘1’ jika J dan K aktif saat HIGH, dan level ‘0’ saat J an K aktif saat RENDAH), flip-flop berperilaku seperti toggle flip-flop, dengan input jamnya melayani sebagai input T. Faktanya, J-K flip-flop dapat digunakan untuk membuat flip-flop lainnya. Itulah mengapa demikian juga kadang-kadang disebut sebagai flip-flop universal. Gambar 10.36 menunjukkan penggunaan J-K flip-flop sebagai T flip-flop.

4. Percobaan [KEMBALI]

Rangkaian klik disini

Video klik disini

Datasheet klik disini

HTML klik disini

0 komentar:

Posting Komentar